- 您现在的位置:买卖IC网 > Sheet目录1193 > AD9985A/PCBZ (Analog Devices Inc)KIT EVALUATION FOR AD9985A

�� �

�

�

�AD9985A�

�The� power-up� default� value� of� PLLDIV� is� 1693�

�CLAMP� TIMING�

�(PLLDIVM� =� 0x69,� PLLDIVL� =� 0xDx).� The�

�AD9985A� updates� the� full� divide� ratio� only� when� this�

�register� is� written� to.�

�CLOCK� GENERATOR� CONTROL�

�05�

�7–0� Clamp� Placement�

�An� 8-bit� register� that� sets� the� position� of� the� internally�

�generated� clamp.�

�When� clamp� function� (Register� 0x0F,� Bit� 7)� =� 0,� a�

�03�

�7–6� VCO� Range� Select�

�Two� bits� that� establish� the� operating� range� of� the� clock�

�generator.�

�VCORNGE� must� be� set� to� correspond� with� the�

�desired� operating� frequency� (incoming� pixel� rate).�

�The� PLL� gives� the� best� jitter� performance� at� high�

�frequencies.� For� this� reason,� to� output� low� pixel� rates�

�and� still� get� good� jitter� performance,� the� PLL� actually�

�operates� at� a� higher� frequency� but� then� divides� down�

�the� clock� rate� afterwards.� Table� 11� shows� the� pixel�

�rates� for� each� VCO� range� setting.� The� PLL� output�

�clamp� signal� is� generated� internally,� at� a� position�

�established� by� the� clamp� placement� and� for� a� duration�

�set� by� the� clamp� duration.� Clamping� is� started� (clamp�

�placement)� pixel� periods� after� the� trailing� edge� of�

�Hsync.� The� clamp� placement� can� be� programmed� to�

�any� value� between� 1� and� 255.�

�The� clamp� should� be� placed� during� a� time� that� the�

�input� signal� presents� a� stable� black-level� reference,�

�usually� the� back� porch� period� between� Hsync� and� the�

�image.�

�When� clamp� function� =� 1,� this� register� is� ignored.�

�divisor� is� automatically� selected� with� the� VCO� range�

�setting.�

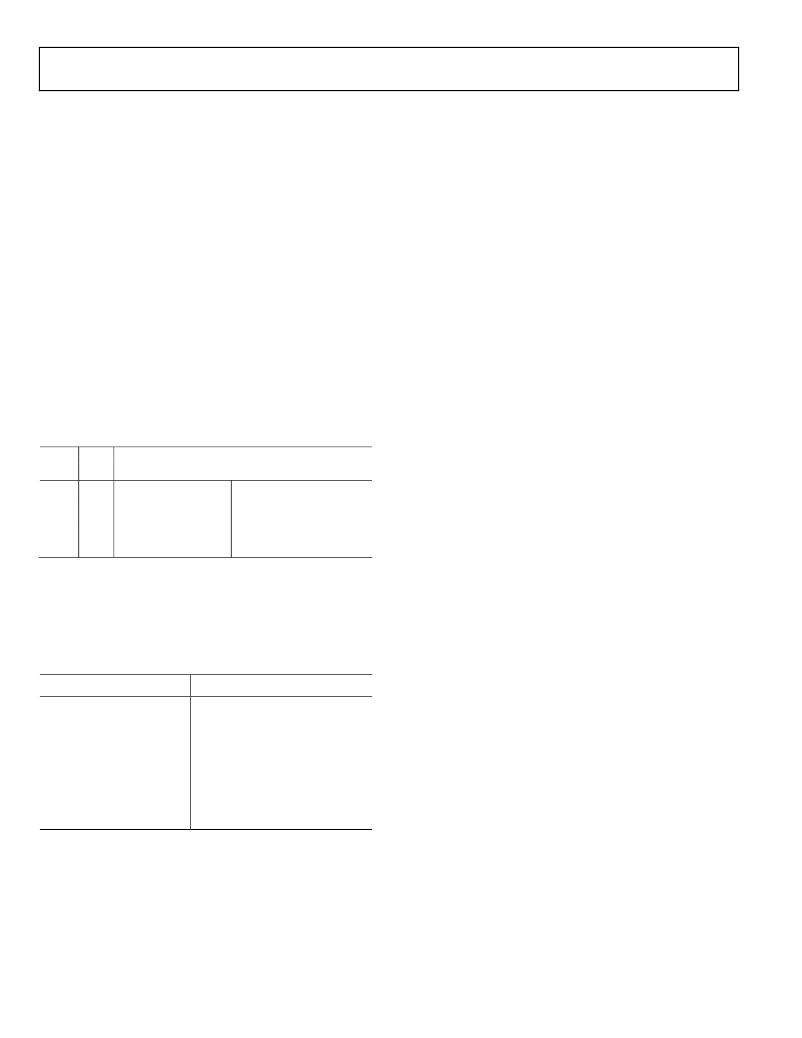

�Table� 11.� VCO� Ranges�

�Pixel� Clock� Range� (MHz)�

�06�

�7–0� Clamp� Duration�

�An� 8-bit� register� that� sets� the� duration� of� the�

�internally� generated� clamp.�

�PV1�

�0�

�0�

�1�

�1�

�PV0�

�0�

�1�

�0�

�1�

�AD9985AKSTZ�

�12� to� 32�

�32� to� 64� (power-up�

�default)�

�64� to� 110�

�110� to� 140�

�AD9985ABSTZ�

�12� to� 30�

�30� to� 60� (power-up�

�default)�

�60� to� 110�

�For� the� best� results,� the� clamp� duration� should� be� set�

�to� include� the� majority� of� the� black� reference� signal�

�time� that� follows� the� Hsync� signal� trailing� edge.�

�Insufficient� clamping� time� can� produce� brightness�

�changes� at� the� top� of� the� screen,� and� a� slow� recovery�

�from� large� changes� in� the� average� picture� level� (APL),�

�03�

�5–3� Current� Charge� Pump� Current�

�or� brightness.�

�Three� bits� that� establish� the� current� driving� the� loop�

�filter� in� the� clock� generator.�

�Current� must� be� set� to� correspond� with� the� desired�

�operating� frequency� (incoming� pixel� rate).�

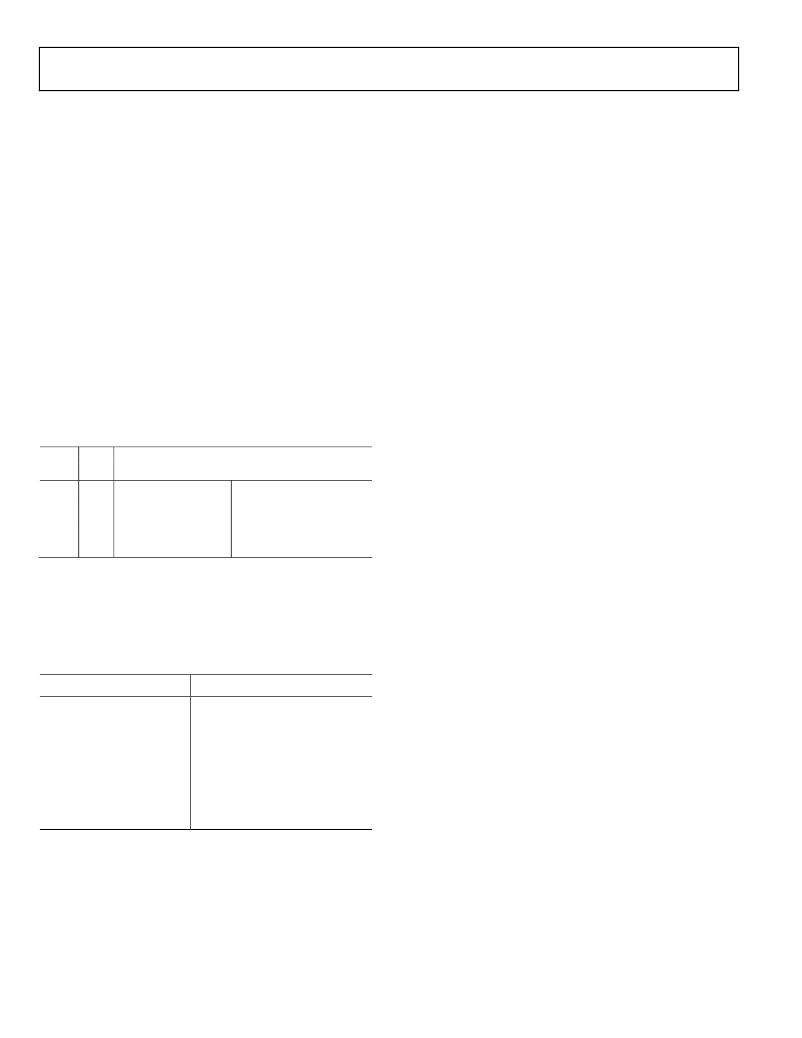

�Table� 12.� Charge� Pump� Currents�

�When� clamp� function� =� 1,� this� register� is� ignored.�

�HSYNC� PULSE� WIDTH�

�07� 7–0� Hsync� Output� Pulse� Width�

�An� 8-bit� register� that� sets� the� duration� of� the� Hsync�

�output� pulse.�

�CURRENT�

�Current� (μA)�

�000�

�001�

�010�

�011�

�100�

�101�

�110�

�50�

�100� (power-up� default)�

�150�

�250�

�350�

�500�

�750�

�The� leading� edge� of� the� Hsync� output� is� triggered� by�

�the� internally� generated,� phase-adjusted� PLL� feedback�

�clock.� The� AD9985A� then� counts� a� number� of� pixel�

�clocks� equal� to� the� value� in� this� register.� This� triggers�

�the� trailing� edge� of� the� Hsync� output,� which� is� also�

�phase� adjusted.�

�INPUT� GAIN�

�111�

�04�

�1500�

�7–3� Clock� Phase� Adjust�

�A� 5-bit� value� that� adjusts� the� sampling� phase� in� 32�

�steps� across� one� pixel� time.� Each� step� represents� an�

�11.25°� shift� in� sampling� phase.�

�08�

�7–0� Red� Channel� Gain� Adjust� (REDGAIN)�

�An� 8-bit� word� that� sets� the� gain� of� the� red� channel.�

�The� AD9985A� can� accommodate� input� signals� with� a�

�full-scale� range� of� between� 0.5� V� and� 1.0� V� p-p.�

�Setting� REDGAIN� to� 255� corresponds� to� a� 1.0� V� input�

�range.� A� REDGAIN� of� 0� establishes� a� 0.5� V� input�

�The� power-up� default� value� is� 16.�

�Rev.� 0� |� Page� 20� of� 32�

�range.� Increasing� REDGAIN� results� in� the� picture�

�having� less� contrast� (the� input� signal� uses� fewer� of� the�

��发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ADA4850-2YCP-EBZ

BOARD EVAL FOR ADA4850-2YCP

ADA4899-1YCP-EBZ

BOARD EVAL FOR ADA4899-1YCP

ADA4937-1YCP-EBZ

BOARD EVAL FOR ADA4937-1YCP

ADA4938-2YCP-EBZ

BOARD EVAL FOR ADA4938-2YCP

ADF37A-KG-TAXB3-R

CONN D-SUB FEMALE 37POS R/A .318

ADG465BRM-REEL7

IC 1CH PROTECTOR 8MSOP

ADG467BR

IC CHAN PROTECTOR OCTAL 18-SOIC

ADISUSBZ

KIT EVAL ADIS W/SOFTWARE USB

相关代理商/技术参数

AD9985AABSTZ-110

制造商:Analog Devices 功能描述:ANALOG INTERFACE FOR FLAT PANEL DISPLAYS - Bulk

AD9985AAKSTZ-110

制造商:Analog Devices 功能描述:ANALOG INTERFACE FOR FLAT PANEL DISPLAYS - Bulk

AD9985AAKSTZ-140

制造商:Analog Devices 功能描述:ANALOG INTERFACE FOR FLAT PANEL DISPLAYS - Bulk

AD9985ABSTZ-110

功能描述:IC INTERFACE 8BIT 110MSPS 80LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:- 特色产品:NXP - I2C Interface 标准包装:1 系列:- 应用:2 通道 I²C 多路复用器 接口:I²C,SM 总线 电源电压:2.3 V ~ 5.5 V 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:剪切带 (CT) 安装类型:表面贴装 产品目录页面:825 (CN2011-ZH PDF) 其它名称:568-1854-1

AD9985AKSTZ-110

功能描述:IC INTERFACE 8BIT 110MSPS 80LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:- 特色产品:NXP - I2C Interface 标准包装:1 系列:- 应用:2 通道 I²C 多路复用器 接口:I²C,SM 总线 电源电压:2.3 V ~ 5.5 V 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:剪切带 (CT) 安装类型:表面贴装 产品目录页面:825 (CN2011-ZH PDF) 其它名称:568-1854-1

AD9985AKSTZ-140

功能描述:IC INTERFACE 8BIT 140MSPS 80LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:- 特色产品:NXP - I2C Interface 标准包装:1 系列:- 应用:2 通道 I²C 多路复用器 接口:I²C,SM 总线 电源电压:2.3 V ~ 5.5 V 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:剪切带 (CT) 安装类型:表面贴装 产品目录页面:825 (CN2011-ZH PDF) 其它名称:568-1854-1

AD9985BST-110

制造商:Analog Devices 功能描述:110 MSPS/140 MSPS ANLG INTRFC FOR FLAT PNL DISPLAYS 80LQFP - Bulk

AD9985BSTZ-110

功能描述:IC INTERFACE 8BIT 110MSPS 80LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:- 特色产品:NXP - I2C Interface 标准包装:1 系列:- 应用:2 通道 I²C 多路复用器 接口:I²C,SM 总线 电源电压:2.3 V ~ 5.5 V 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:剪切带 (CT) 安装类型:表面贴装 产品目录页面:825 (CN2011-ZH PDF) 其它名称:568-1854-1